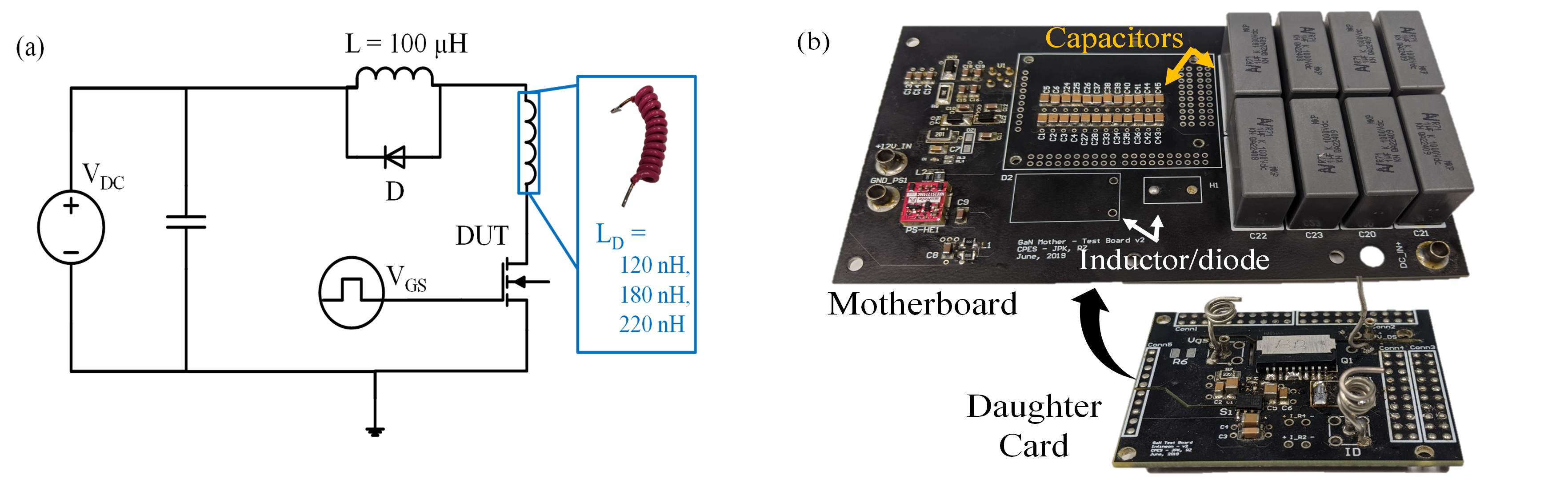

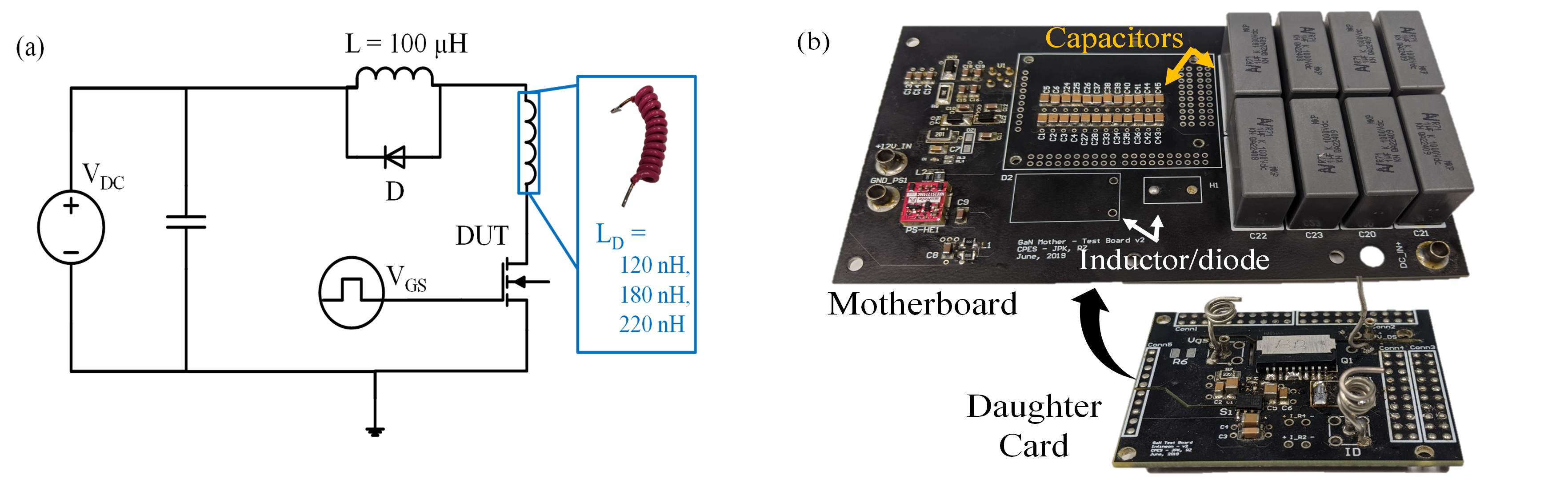

Fig. 1. Clamped inductive switching circuit schematic and external parasitic inductance (a), the experimental test circuit that includes the motherboard for the primary power loop and the daughter cards for the minimized gate driver loop and sensing circuitry (b).

An essential ruggedness characteristic of power devices is the capability to withstand the transient overvoltage in power electronic applications. As the newly commercialized GaN HEMTs can switch faster under higher voltage biases, it is important to identify their true overvoltage limitations in transient switching events. This work characterizes the transient overvoltage capability and failure mechanisms of GaN HEMTs under hard-switched, turn-off conditions at increasing temperatures, by using a clamped inductive switching circuit with a variable parasitic inductance as shown in Fig. 1(a). This test method allows flexible control over both the magnitude and the dV/dt of the transient overvoltage. The overvoltage robustness of two commercial enhancement-mode (E-mode) p-gate HEMTs was extensively studied: one with the Ohmic-type gate (HD-GIT) and the other with the Schottky-type gate (SP- HEMT). The experimental motherboard-daughtercard system is shown in Fig. 1(b).

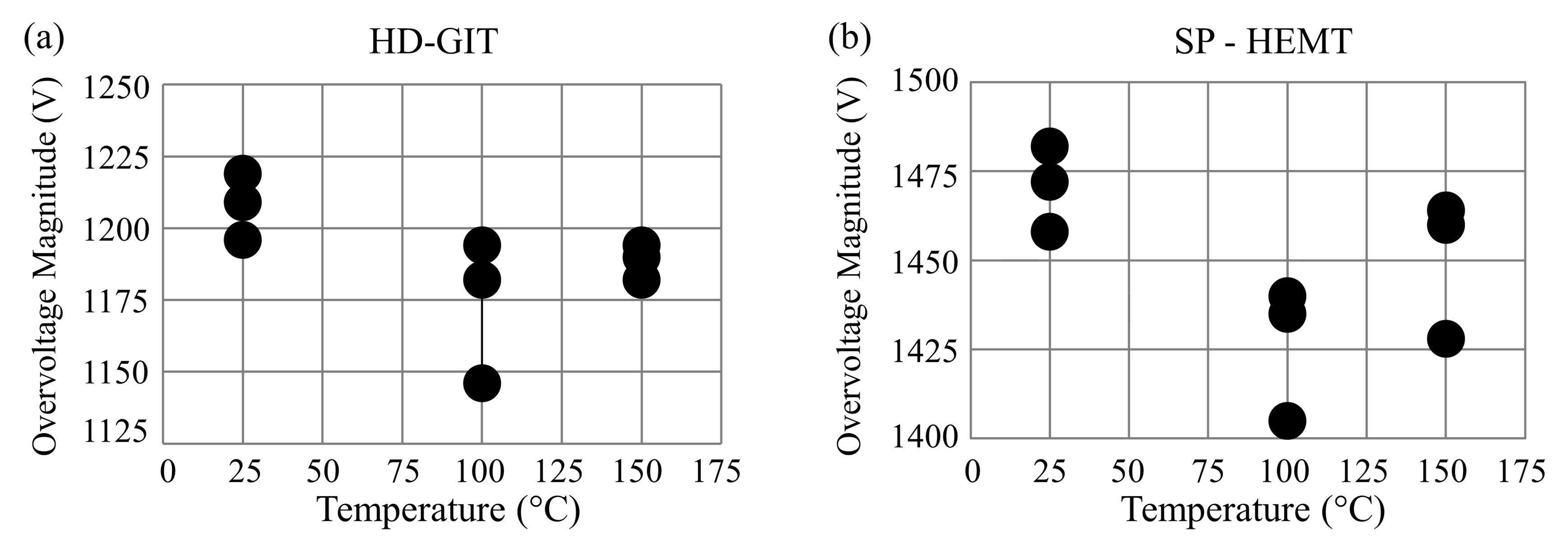

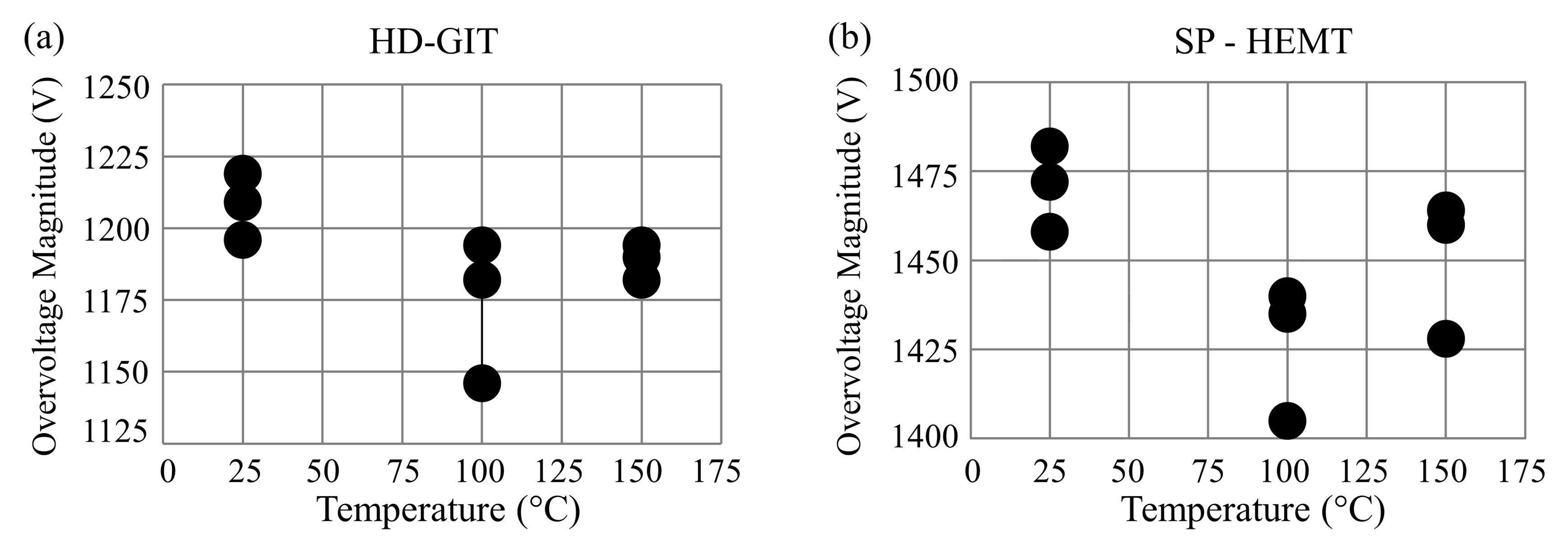

Tests were conducted with varying parasitic inductance (LD) values and increasing current values to measure the overvoltage magnitude. The failure of the two devices was found to be determined by the overvoltage magnitude rather than the dV/dt. Tests were then repeated with LD = 130 nH but at increasing temperatures (100° C and 150° C). The failures of both devices were consistent with room temperature results and results are shown in Fig. 2. Overall, this work shows the robustness of two commercially available p-Gate GaN HEMTs under overvoltage switching stresses and increasing ambient temperatures.

Fig. 2. Overvoltage failure magnitudes measured at different temperatures for the HD-GIT (a) and SP-HEMT (b).