LIBRARY

Active Control and Gate-Driver Design for Voltage Balancing of Both MOSFETs and Body-Diodes in Series-Connected SiC MOSFETs

To guarantee the balance voltage sharing under both MOSFET and body diode conducting period, this work proposes to apply different active voltage balance strategy in different period: 1) In body diode conducting period, to solve the voltage unbalance caused by dv/dt difference, extra short-pulse gate signal (SPGS) on the device with a higher turn-off voltage is proposed, which controls the MOSFET channel current to affect the voltage sharing; 2)In MOSFET conduct-ing period, to solve the impact of gate signal mismatch, active gate signal delay time (GSDT) control to mitigate the time mismatch on gate signal. The SPGS with fixed duration is also ap-plied in MOSFET conducting period to eliminate the impact of dv/dt difference on the GSDT control.

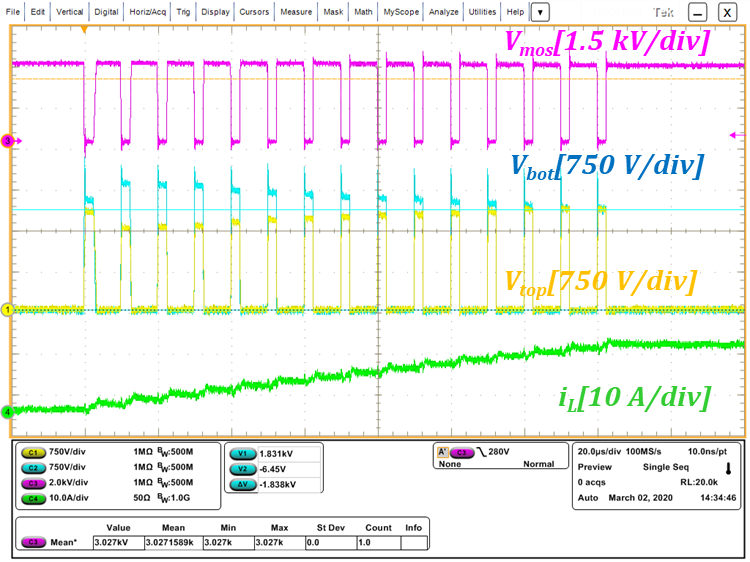

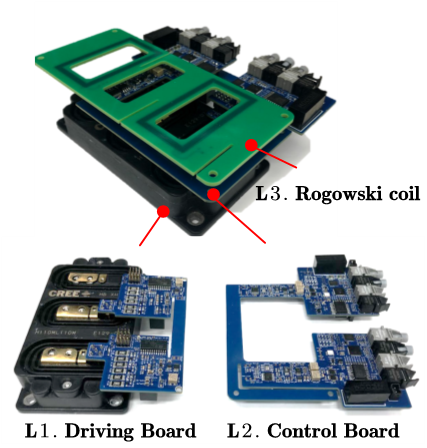

To implement the proposed voltage balancing method, a new gate driver (as shown in Fig. 1) is designed, with improvement on the turn-off voltage sensing and gate signal control. Experiments with two series-connected 10 kV SiC MOSFETs under different conditions are conducted and the results verify the proposed voltage balancing method. Fig. 2 shows the transient that the voltage sharing of diodes are balanced by the closed-loop control.