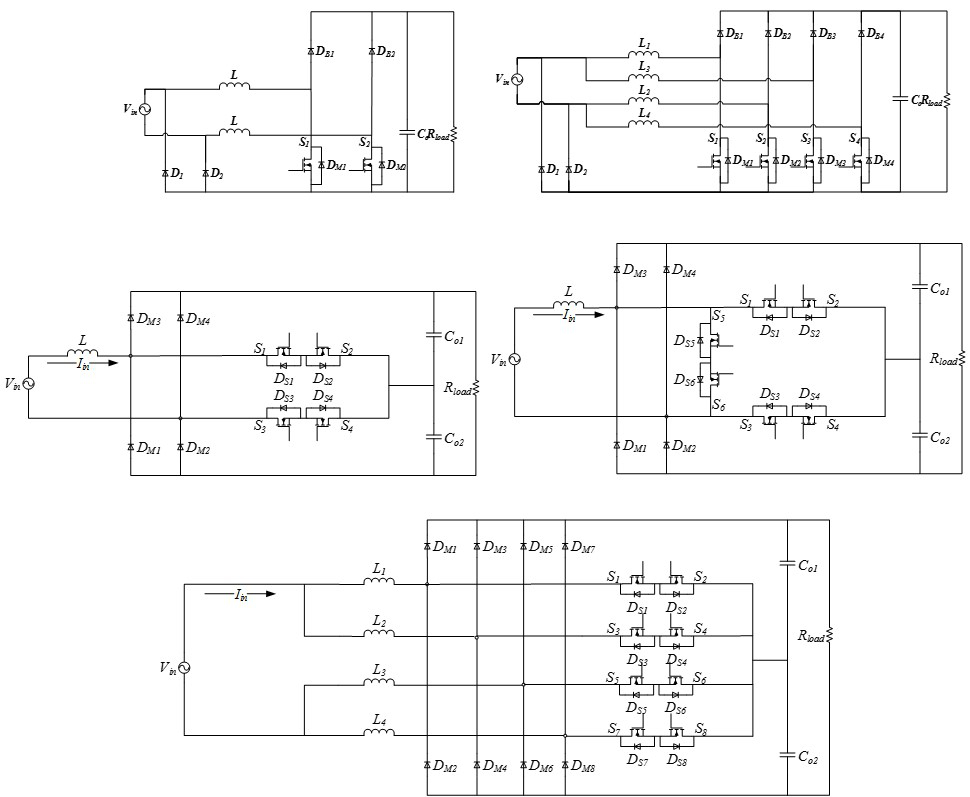

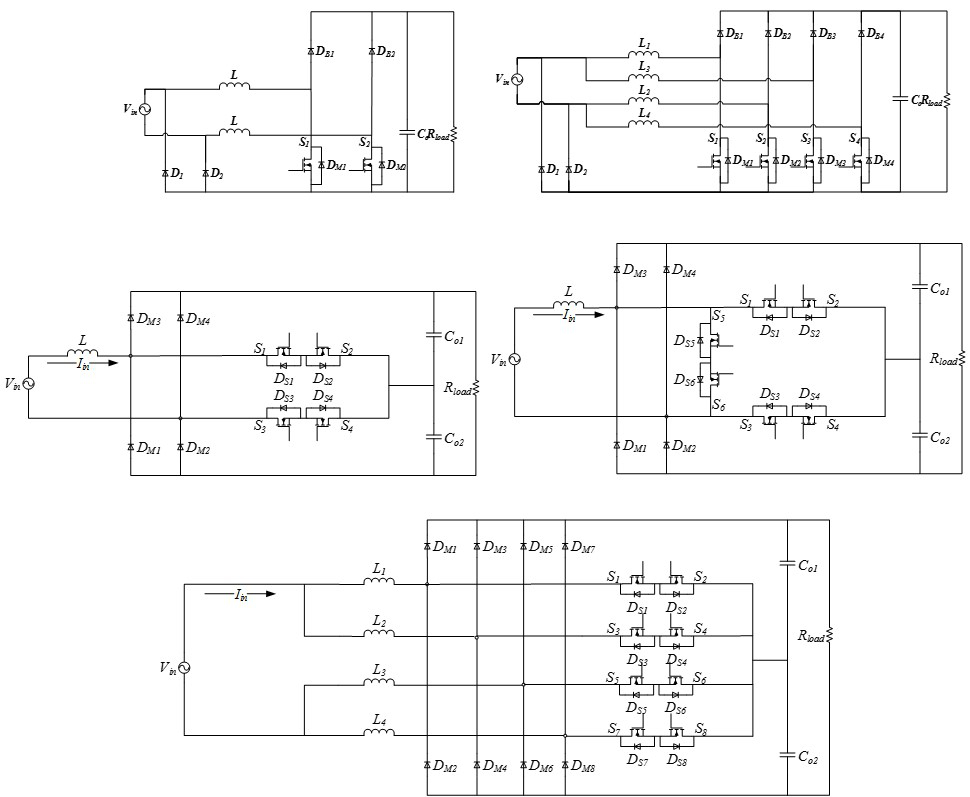

Fig. 1. (a) Semi-bridgeless PFC boost rectifier. (b) Paralleled or interleaved PFC boost rectifier. (c) Three-level bridgeless PFC boost rectifier. (d) Three-level bridgeless PFC boost rectifier with AC switch. (e) Paralleled or interleaved Three-level bridgeless PFC boost rectifier.

Increasing the efficiency has always been one of the most important topics in power electronics, besides power density increase and cost reduction. Recently, to improve the efficiency of the front-end PFC rectifiers for medium power applications such as telecom, the more-electric aircraft and the electric vehicle, industry has begun to look into bridgeless PFC rectifiers due to the efficiency increase brought by the absence of the diode bridge. In this paper, the efficiency of a two-level semi-bridgeless PFC boost rectifier (2LPFC) with clamping, a paralleled two-level semi-bridgeless PFC boost rectifier (P2LPFC) with clamping, an interleaved two-level semi-bridgeless PFC boost rectifier (I2LPFC) with clamping, a three-level bridgeless PFC boost rectifier (3LPFC), a three-level bridgeless PFC boost rectifier with AC switch (3LPFCAC), a paralleled three-level bridgeless PFC boost rectifier (P3LPFC) and an interleaved three-level bridgeless PFC boost rectifier (I3LPFC) are evaluated and compared. The topologies in question are shown in Fig. 1.

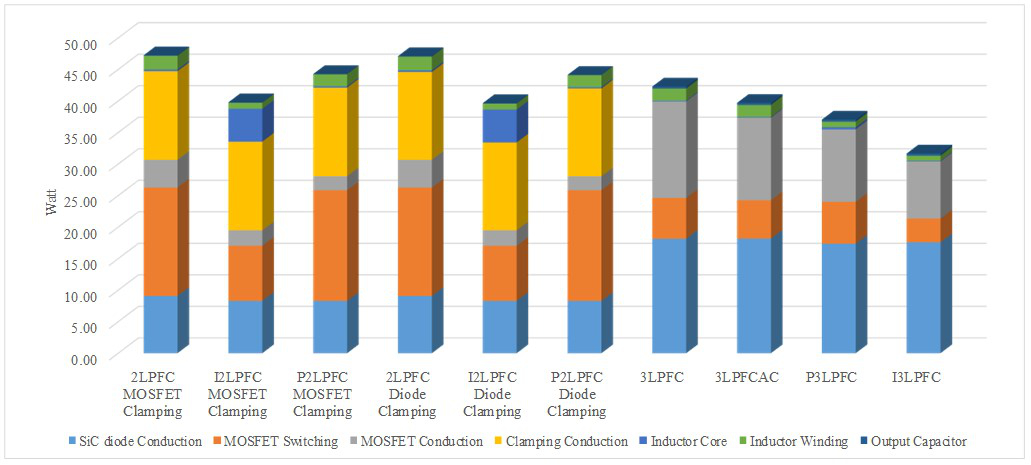

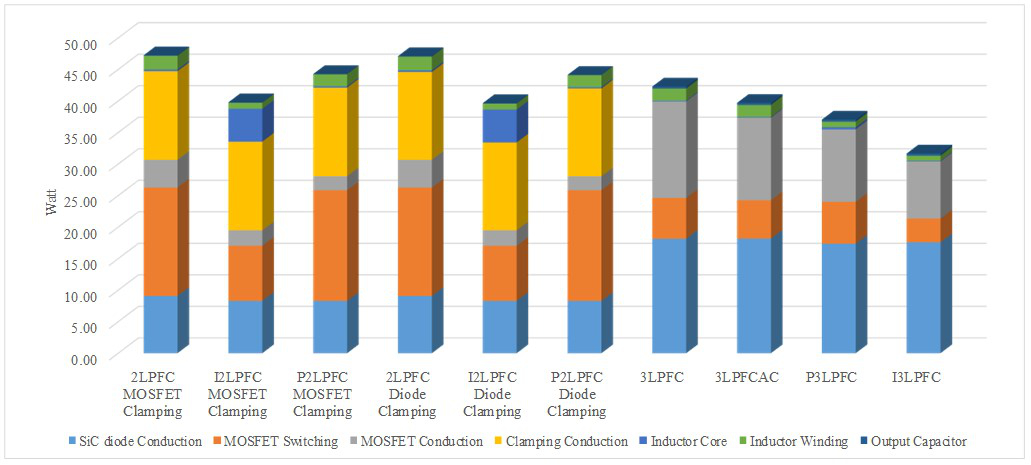

To estimate the efficiency of each converter, the operation of all the converters are first introduced and analyzed. Based on this, to make a fair comparison, an efficiency-oriented design optimization is conducted to all the converters. After that, the efficiency estimation is done by simulation and mathematical calculation. To be more specific, the conducting current at any time through any components can be obtained using simulation based on which the conduction loss can be calculated taking into consideration such factors as temperature. To estimate the switching loss of the switches, a piecewise linear model for MOSFET is applied. In this model, the gate charges of the MOSFET instead of the non-linear capacitance are used to calculate the turn-on and turn-off time due to the consistency of the charges in a wide voltage range. The loop inductors and the loss caused by charging the diode when turning on the switch is considered. Transition of the drain-to-source current and voltage are assumed to be linear. The efficiency comparison of the topologies is shown in Fig.2.

Fig. 2. Loss breakdowns of the compared topologies.