LIBRARY

Avoiding Si MOSFET Avalanche in Cascode Device and Achieving Zero-Voltage-Switching for Cascode Device

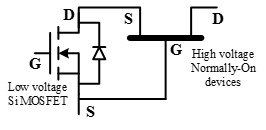

The cascode structure shown in Fig. 1 is used to make the terminal a normally-off device. The Si MOSFET controls the on/off state of high-voltage normally-on devices. The interaction and parasitic capacitance of the two devices plays an important role in achieving high efficiency, especially under soft-switching conditions. The two devices should be well matched. Otherwise, the Si MOSFET may have an avalanche breakdown during the turn-off process. Although the avalanche voltage of Si protects the high-voltage normally-on device from the damage of over-voltage, avalanche is not recommended operation for the Si MOSFET, and it is a potential risk to the reliability of the device. The energy dissipated through the avalanche path brings additional loss. Moreover, the avalanche of an Si MOSFET will break the charge balance of the parasitic capacitors of the MOSFET and the high-voltage normally-on device, which will cause the device to lose its zero-voltage turn-on condition internally during the soft-switching turn-on process. This is undesirable, especially in applications that operates at MHz frequency.

After analyzing the voltage distribution process of the cascode device in detail, and quantifying the conditions under which Si will reach avalanche and the avalanche loss, we have devised a simple and effective solution which is paralleling an external capacitor with drain-source of Si MOSFET to compensate the junction capacitors charge mismatch and thus avoid Si reaching avalanche. This solution also achieves zero-voltage-switching for high-voltage, normally-on devices.