LIBRARY

System Two-stage VR for future server microprocessors (2003)

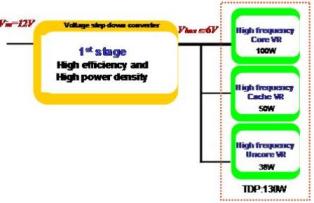

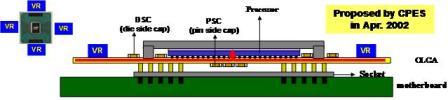

In this arrangement, the VR has to be very small to be put on the VR board, so high frequency VR (e.g. 1MHz) is required. However, the efficiency of the current single stage VR suffers at high frequency. The best way to realize this approach is to employ the two-stage architecture for MHz frequency operating capability. Moreover, since the server microprocessor needs three different voltages, by taking advantage of the TDP spec of the server microprocessor, we can apply the system two-stage architecture, as shown in Figure 2, to reduce the power rating of the first stage for further cost and size reduction. In this structure, the first stage only needs to design at 130W power for the three VRs due to the TDP in the server microprocessors. Interconnection effect is minimized by putting VR on the OLGA board. Comparing with 600kHz single stage VR which is for today's server VR, 1MHz two-stage VR with voltage divider as the 1st stage can achieve 1% higher full load efficiency and 45% output filter footprint reduction.