LIBRARY

Development of a Power Hardware-in-the-Loop Induction Machine Emulator

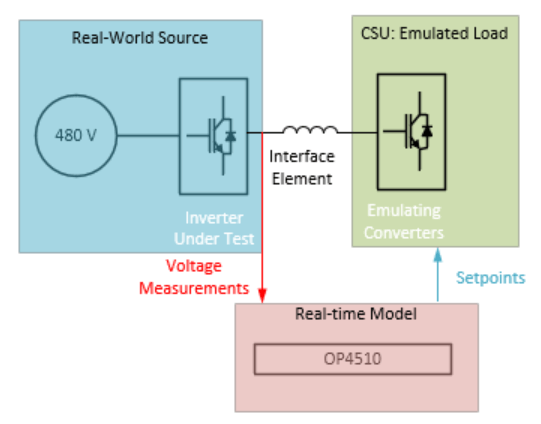

Key efforts in this work focus around the modeling of the induction machine and the design and selection of the inductor that interfaces between the real-world source and the CSU. The traditional arbitrary reference frame model of the induction motor leads to current setpoints, but in this work the setpoints are also formulated to allow the CSU to emulate the back-emf of the machine in series with a resistor and inductor. By modeling the induction motor as a back- emf, the interface inductor becomes an essential part of the model.

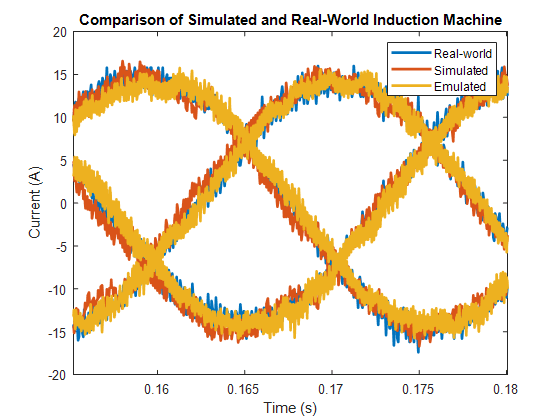

Fig. 2 shows the close matching between the real-world, simulated, and emulated machines with the CSU running in back-to-back mode. The CSU is made up of six four-quadrant amplifiers. In the back-to-back case, three of the amplifiers are emulating a voltage source, and another set of three is emulating the induction machine as a current sink. This validates the models and the CSUs perfor- mance, and the next step in the research is to run with the external drive connected to the amplifier.

P-HIL emulation of induction motors allows the drive to be tested under full power conditions before a motor has been fully developed. This allows significant improvements in the design process. Furthermore, different induction machines can be emulated on the same P-HIL hardware platform by changing only the machine model parameters. This paper details an induction machine emulator utilizing the P-HIL concept. Design details including the modeling approach, interface inductor selection, design, and fabrication, and system testing are presented in the full paper.