LIBRARY

High Power Density 1MHz 3kW 400V-48V LLC Converter for Datacenters with improved Core Loss and Termination Loss

Using a matrix transformer helps to reduce the conduction loss of the secondary winding and SR but also increases the core loss since all elemental transformers are subject to the same volt-sec. Hence, there is a trade-off between the conduction loss and core loss when it comes to designing a matrix transformer. Three candidates of Matrix transformer have been considered: a single transformer, two transformers, and four transformers. The three candidates are evaluated based on the total winding and core loss vs. footprint. The two-transformer solution was deemed better. The two elemental transformers are then integrated in a UI core structure. However, at 1 MHz and single secondary turn winding (High Volt-sec per turn). The transformer core suffers from dimensional effects like non-uniform flux and increased eddy core loss. In order to limit the eddy core loss, the transformer core is designed using a thin rectangular core instead of a round shape core. This method reduces the core loss by around 4 W.

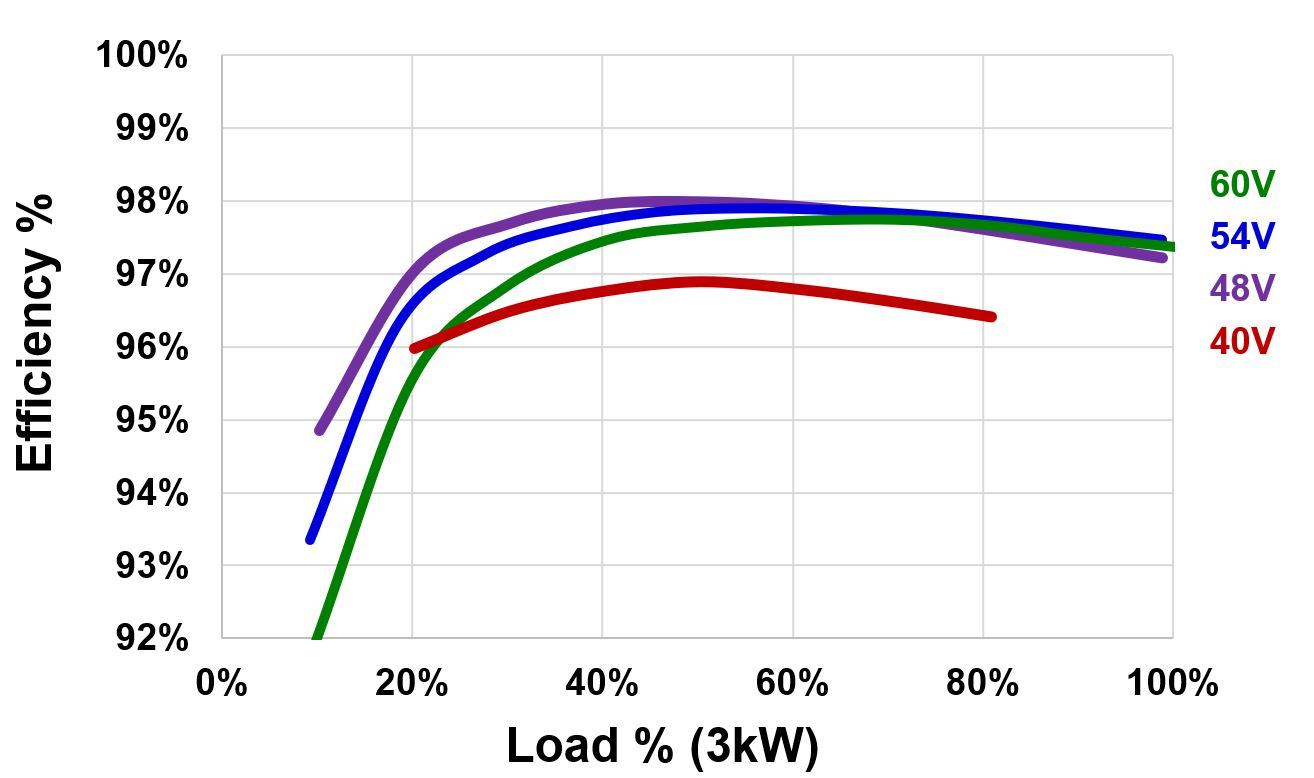

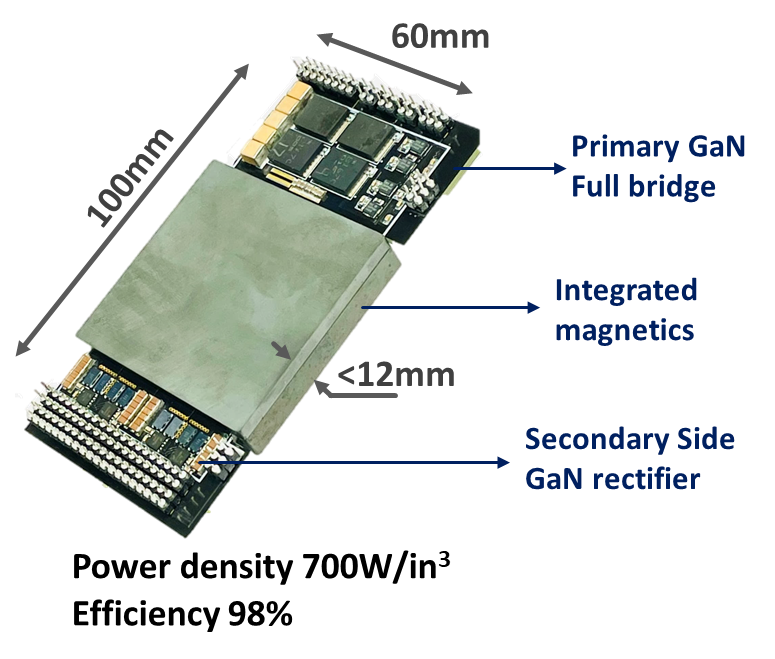

The converter is implemented on 6-Layer PCB, 2 oz. copper. 35 m?-600 V GaN devices are used for the primary Half-bridge, and 4 m?, 80 V GaN devices are used for the secondary center-tap rectifiers. Fig 1. shows the implemented PCB including primary and secondary devices and gate drivers and magnetics. The converter 11mm profile has a power density of 700W/in3. Fig. 2 shows the tested efficiency of 98% at 54 output voltage.

In summary, in this paper, the impact and importance of dimensional effects on core loss for a high-power transformer running at high frequency is discussed. Different candidates of matrix transformers are evaluated. a matrix of two transformers implemented on UI core with elongated core shape to reduce core's eddy loss. Prototype of the proposed converter is demonstrated. In the final paper, another part will be added to discuss the termination loss of SR and how to reduce it with optimized device layout.