LIBRARY

Hybrid Voltage Balancing Approach for Series-Connected 10 kV SiC MOSFETs for DC-AC Medium-Voltage Power Conversion Applications

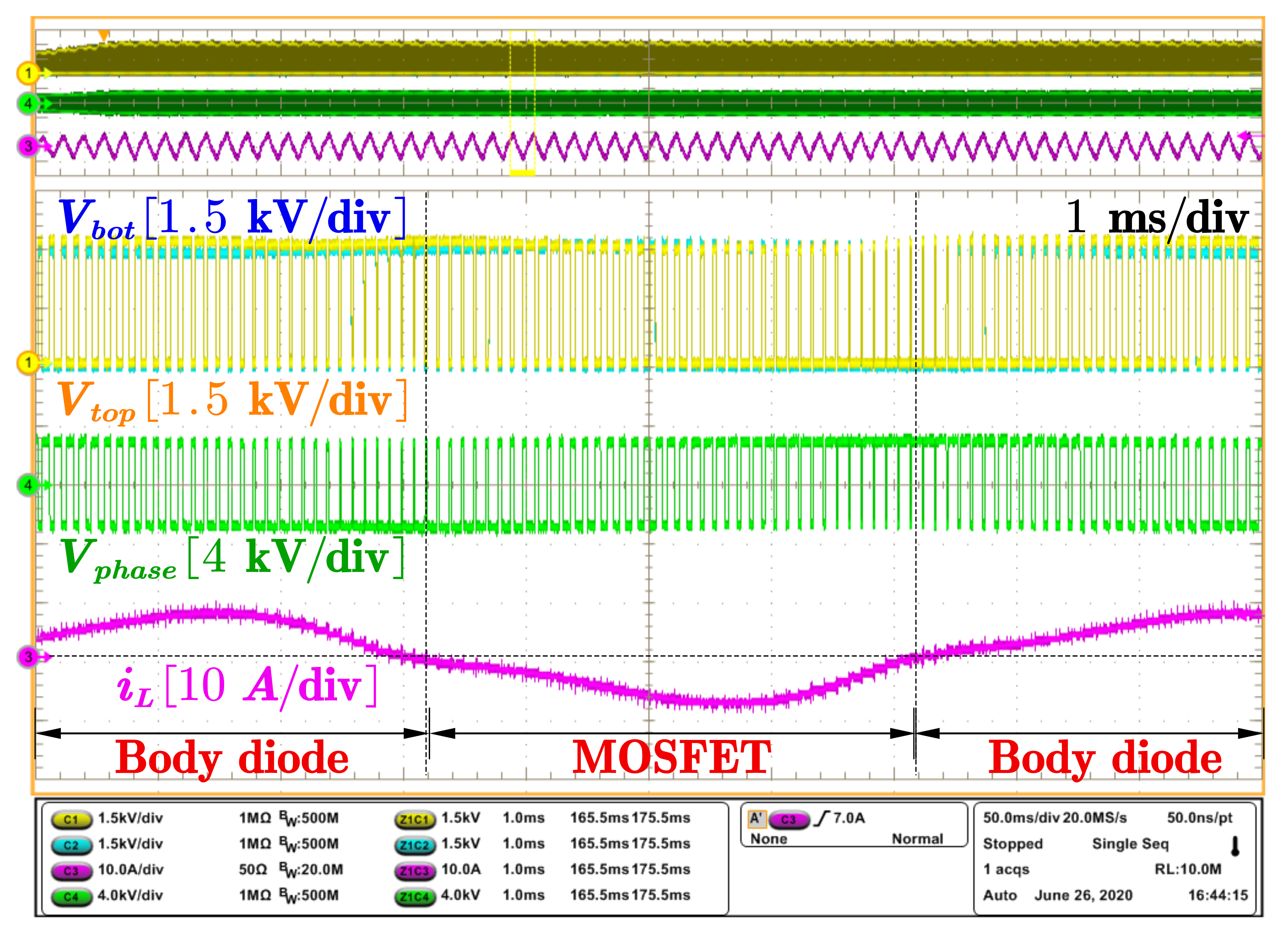

In this work, the delay time control is first evaluated to mitigate the voltage unbalance caused by parasitic capacitors. The analysis shows that active voltage balancing control has a limitation to adjust delay time accurately under a wide range of load current and cannot solve the voltage unbalance of body diodes. To mitigate the impact of a parasitic capacitor, the unbalanced parasitic capacitor from the package is first measured and compensated with the external capacitor. The value of added compensation capacitor is less than 100 pF and has slight impact on the total switching loss.

In the meantime, close-loop delay time adjustment also includes to mitigate the possible mismatch of gate signal. Body-diode turn-off detection also investigates with local drain-source voltage measurement circuit on the gate driver, so the delay time adjustment will be suspended during body diode turn-off period. Fig. 1 shows the experiment result with the proposed hybrid voltage- balancing approach, which demonstrates a well-balanced voltage sharing for both MOSFET period and body diode period.