LIBRARY

A Systematic Parasitic Capacitance Extraction Procedure for Three-Level Neutral-Point-Clamped Inverter Modules

For a converter circuit with discrete power, the semiconductor's stray capacitances can be determined by their 3D finite analysis (FEA) model or analytical calculations of their discrete packaging. However, for power-module-based converter designs, the parasitic capacitance is extracted by destructive physical measurements or layout inspection in prior literature. This work develops a cost-effective and accurate procedure for module parasitic capacitance extraction by simply estimating the parasitic capacitances from the ringing frequency of the CM current in the proposed extended double-pulse test (eDPT) setup. In this work, a three-level neutral-point-clamped (3L-NPC) module (APTMC 60TLM55CTAG) from Microsemi is used to demonstrate the parasitic extraction process.

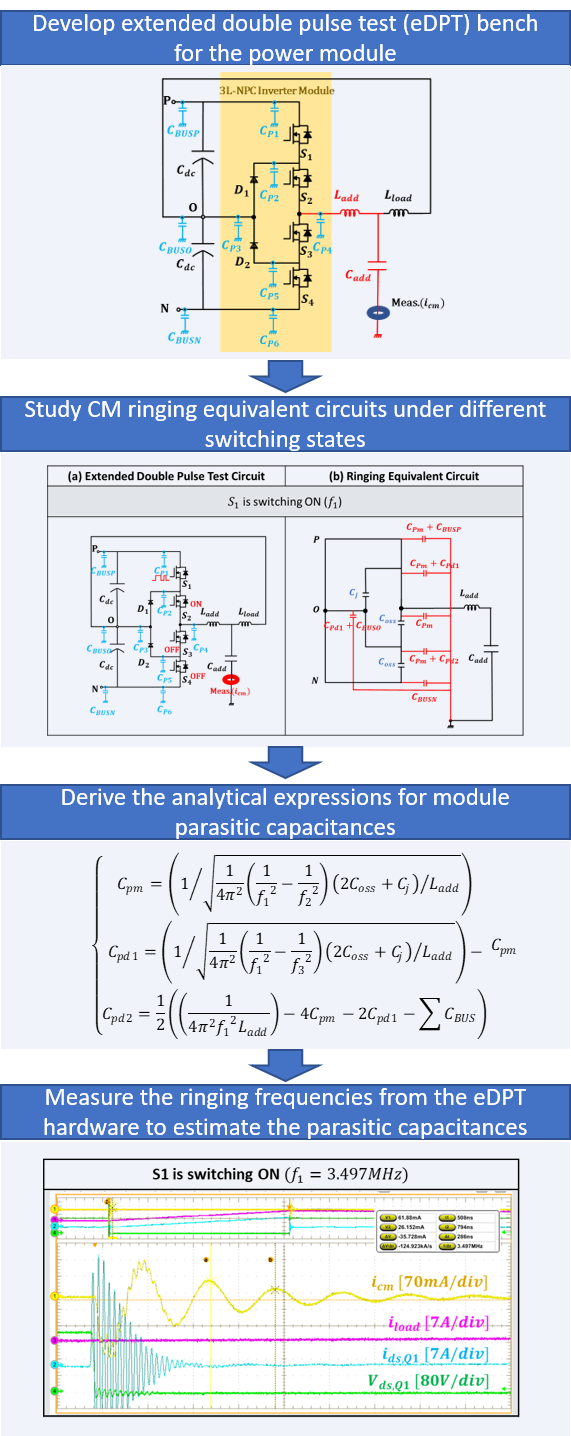

The proposed eDPT circuit and parasitic capacitance extraction process is detailed in Fig. 1. An additional large inductor and capacitor are introduced between the output and load of the conventional DPT circuit of 3L-NPC modules to mask the impact of the stray inductance and to shunt and circulate the high-frequency CM current (icm), respectively. The analytical expressions for estimating the parasitic capacitance are then derived based on the equivalent CM circuit of the eDPT circuit under different switching states.

The estimated parasitic capacitances show good accuracy compared to conventional open-module measurement results, and the CM currents created specifically by the inverter's CM parasitic components are validated by a full-scale three-phase DC-AC process. This systematical procedure can facilitate the process of EMI prediction for electromagnetic compatibility (EMC) engineers and can also be further extended to higher-level multichip modules.