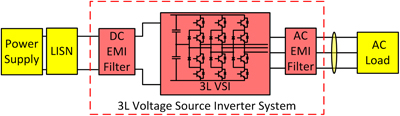

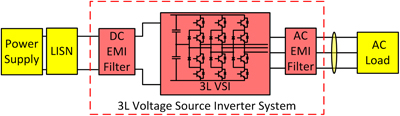

Fig. 1. Three level voltage source inverter system.

The voltage-source pulse-width modulation (PWM) inverter has made a significant contribution to achieving energy conservation and improving system performance in many applications. Compared with two level voltage source inverters, neutral-point-clamped (NPC) inverters can achieve better performances on ripples, harmonics and EMI. The common mode elimination (CME) modulation is a well-known modulation method which can theoretically eliminate the common mode voltage. However, in the real implementation, due to the existence of dead time (DT) which avoids the shoot through problem during operation, the real benefit from CME modulation is limited and the penalty on voltage utilization ratio and the loss of neutral voltage balancing capability make this modulation method less practical.

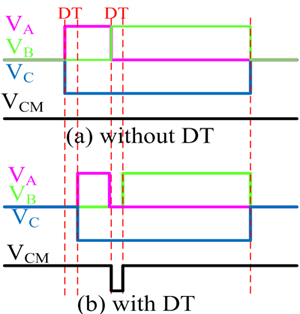

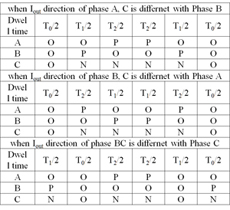

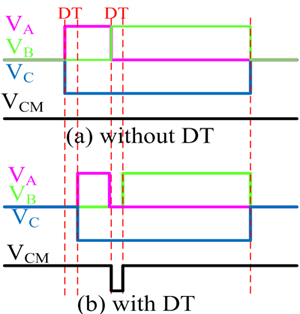

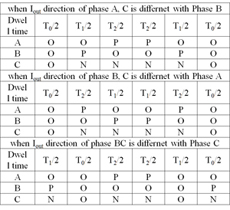

To overcome the penalty for adding DT, an improved compensation method is proposed, based on the switching states analysis of each 3L phase leg. The impact of DT on CM voltage generation can be calculated as shown in Fig.2. To eliminate this impact, the vector sequence in CME modulation can be adjusted based on the current direction of the three phases.

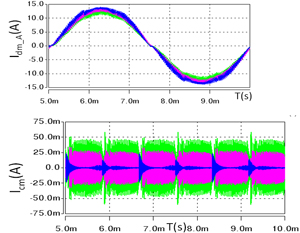

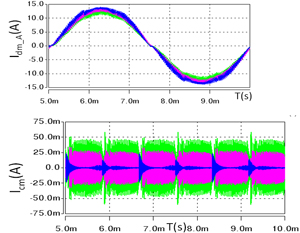

Verification results show that the CM noise can be reduced significantly with this compensation method. However, there will be more distortion in the output current.

Fig. 2. Impact of DT on CM voltage generating in one swithcing period.

Fig. 3. Vector sequence selection of ICME in section 1.

Fig. 4. System test results; With0.5us DT: pink; with 1us DT: Green, with 1usDT and DTcompensation : blue.