LIBRARY

Spurious Turn-On inside a Power Module of Paralleled SiC MOSFETs

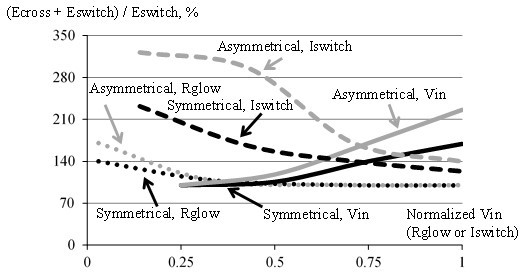

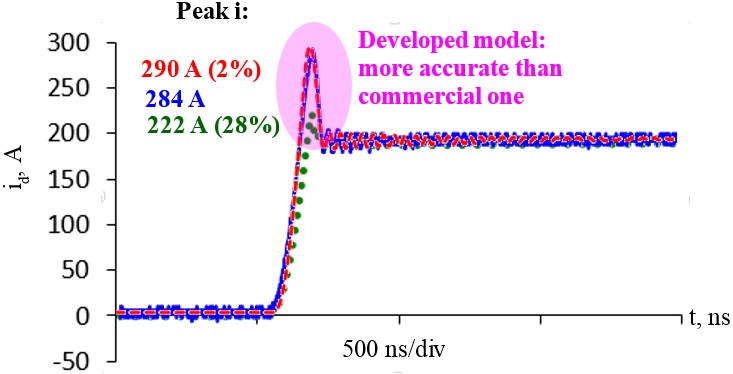

The SPICE model of one commercial module is developed and verified with a higher accuracy than the commercial SPICE model. The total switching energy and susceptibility to cross-turn-on for two modules tailored from the commercial layouts are investigated by studying the simulated channel current of each MOSFET die and terminal current of the module in the presence of packages' parasitic impedances. The total switching energy which is the sum of the switching energy and extra energy induced by cross-turn-on of the asymmetrical module can be as high as 322% of the conventionally defined switching energy, which clarifies severity of cross-turn-on for the high-voltage and fasting-switching application of paralleled SiC MOSFETs.

A symmetrical layout decreases extra energy induced by cross-turn-on while maintaining a similar total switching energy under a low input voltage (< 400 V) application and a lower total switching energy under a high input voltage (> 400 V) application as compared to an asymmetrical layout. The symmetrical layout significantly reduces the peak cross-turn-on current stress on die, which is only 10.6% of the current for the asymmetrical case. Besides the layout symmetry, a paralleling SiC Schottky diode also reduces cross-turn-on current to 21.3% of the original value. Decreasing the gate and Kelvin-Source inductance doesn't greatly mitigate the problem and increasing external gate resistance suppresses cross-turn-on at the expense of a higher total switching energy.