LIBRARY

Dynamic Voltage Balancing Method for Fast-Switching SiC MOSFETs with High dV/dt Rates

Due to the limited availability of silicon-carbide (SiC) metal-oxide semiconductor field-effect transistors (MOSFETs) at medium voltages, using multilevel topologies or stacking individual semiconductors in a series could be possible solutions which take advantage of the superior properties featured by SiC MOSFETs at high voltages.

Multilevel converters are formed by connecting individual semiconductors in different structures, enabling operation at higher voltages and currents than the rating of single devices. These converters have been the scope of a tremendous amount of research due to their outstanding advantages including low common-mode voltages, low dV/dt stresses, low propagated electromagnetic interference (EMI) emissions, and high efficiency. As a result, multilevel converters have been employed in a wide variety of applications such as grid-tied inverters, active front-end rectifiers, high-voltage direct current, motor drives, flexible ac transmission systems, etc.

Although multilevel converter topologies are reliable and feature notable advantages, their size and cost are much larger compared to stacked semiconductors. According to the literature, using more than one medium-voltage semiconductor in series leads to better on-resistance than using a single higher-voltage device. Also, smaller on-resistance, stacked low-voltage semiconductors feature a lower price, lower switching loss, and more accessible peripherals (such as gate drivers) compared to a single higher-voltage switch.

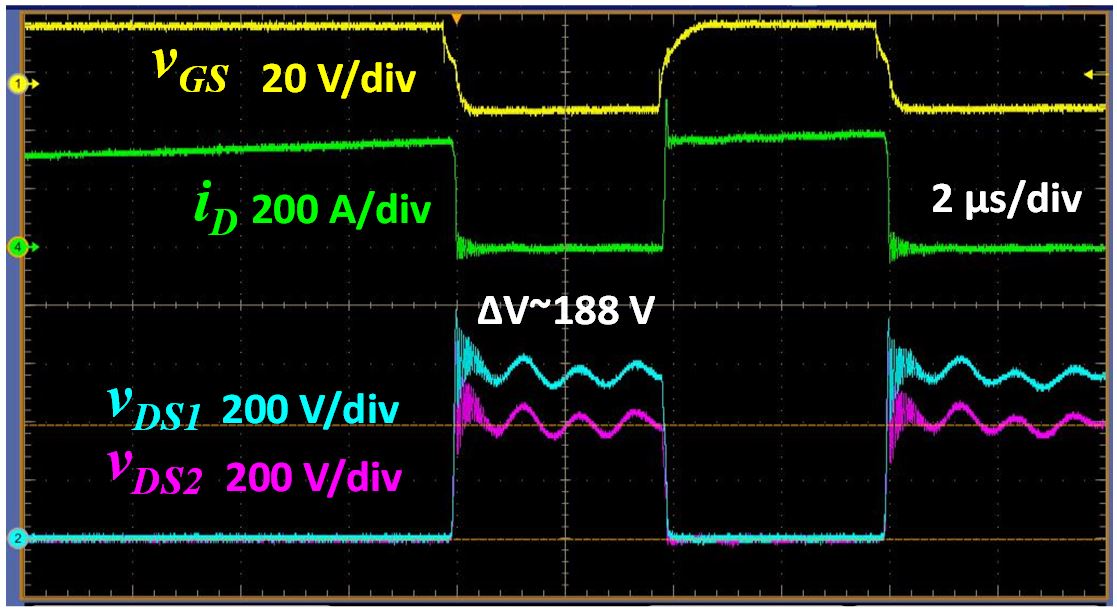

This paper presents a novel method for dynamic voltage balancing among stacked SiC MOSFETs. The proposed scheme is capable of achieving nearly perfect dynamic voltage balance among two stacked 1.7 kV SiC MOSFETs. This method does not add losses to the system, and does not increase the losses of individual devices. Simulations as well as experimental implementation results are provided to prove the effectiveness of the proposed method.