LIBRARY

Rogowski Switch-Current Sensor Self-Calibration on Enhanced Gate Driver for 10 kV SiC MOSFETs

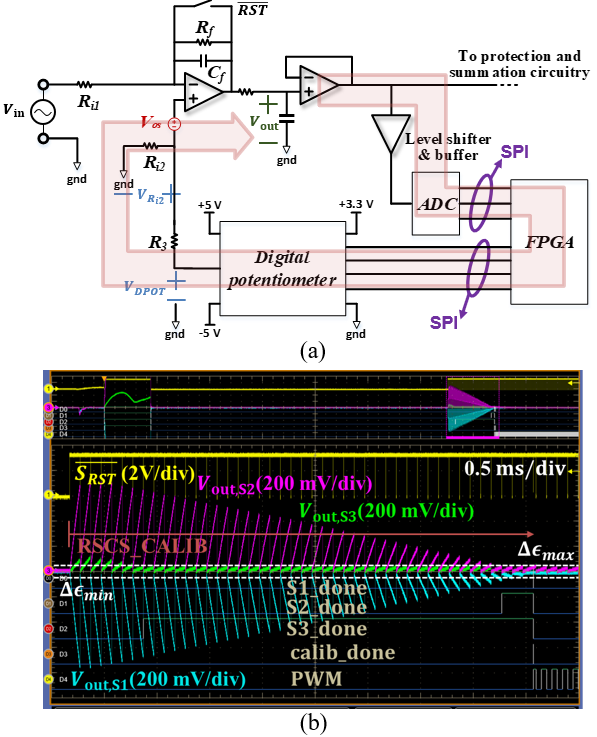

Due to known non-idealities of the OpAmp integrator circuit such as input offset voltage and input bias current, an offset calibration circuit is necessary for successful integrator use. Mechanical potentiometer is not ideal due to temperature swings and mechanical parts that reduce usable lifetime. Generally, electrical parts are more reliable and have longer lifetime. Therefore, digital potentiometer instead analog is proposed. Calibration circuit with ADC, FPGA, and DPOT is implemented during start-up, shown on Fig. 2(a) for one out of three RSCS. SRST sequence is first initiated. Due to existence of non-idealities we will see ramp increasing until the reset occurs. Towards the end of the SRST enable, FPGA will initiate ADC to sample. If sampled value is higher than maximum allowable error, FPGA will reconfigure the digital potentiometer (DPOT), thus reducing the influence of non-idealities in the next cycle. This process will be repeated until the error becomes satisfactory. Verification of the implemented algorithm is shown at Fig. 2(b). Good resolution of the system is achieved, with maximum error of the system of ± 2.5 A. Self-calibration process is finished relatively quickly during start-up, within 12.4 ms maximum.