RESEARCH

Design and Assessment of a Medium-Voltage Power Cell based on High-Current, 10 kV SiC MOSFET Half-Bridge Modules

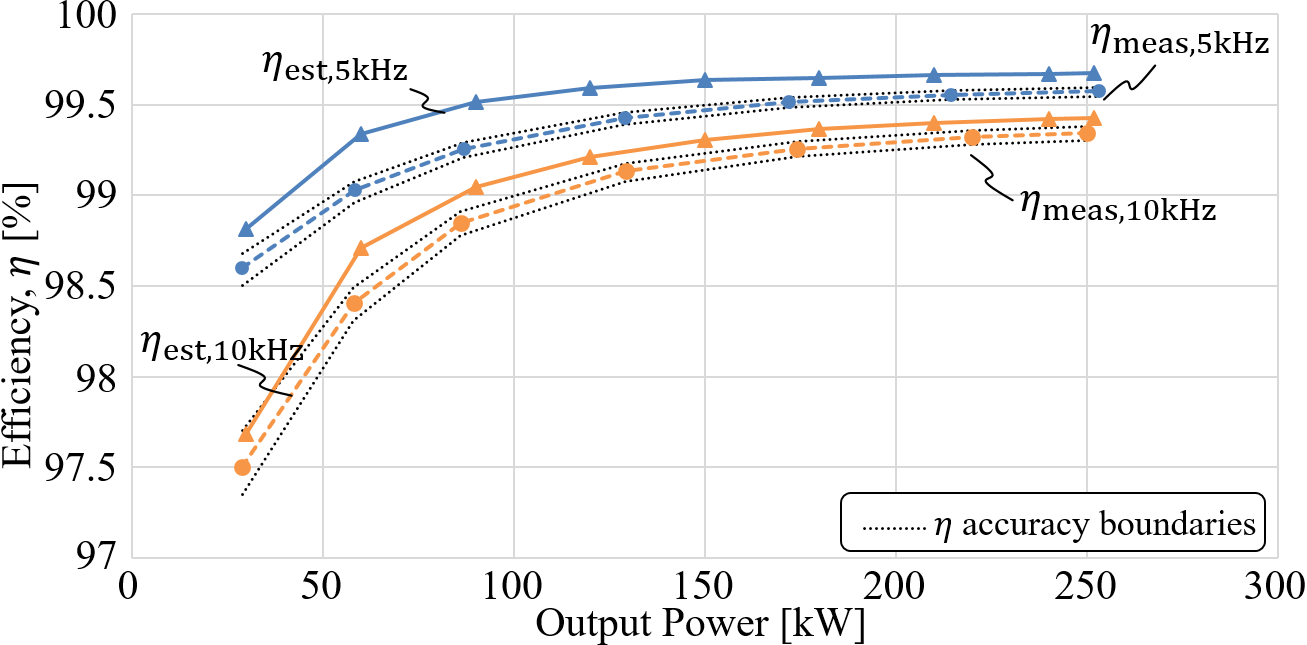

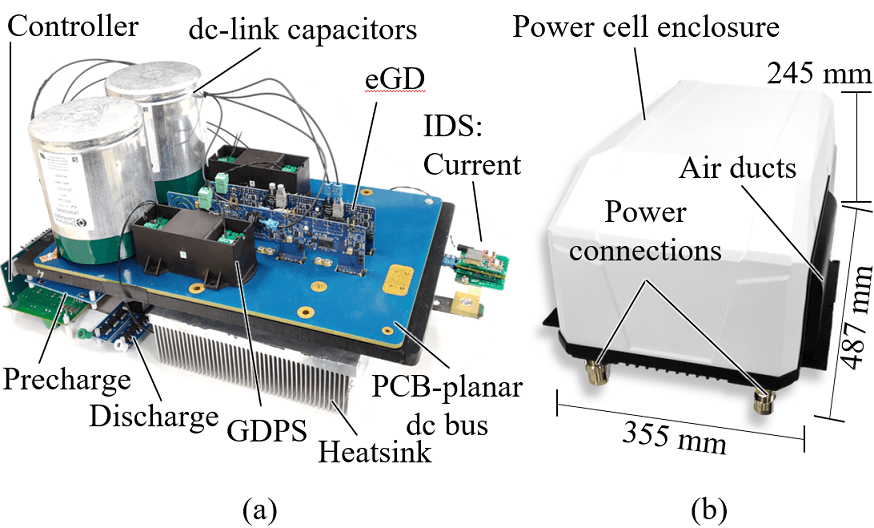

Accordingly, design considerations and available solutions for the design of a power cell utilizing high current, 10 kV, SiC MOSFETs in MV applications is presented. Furthermore, the systematic design and assessment framework process of the power cell is pro- vided. Critical insulation considerations and testing procedures are described, confirming partial-discharge-free (PD‐free) operation at the rated voltage of the power cell. Safe operating area (SOA) is derived for a single dc-dc case with a duty cycle of 50% for a designed cooling system. However, the described methodology would be the same for any case in dc-dc or dc-ac operation mode. The thermal model is 90% accurate, showing an acceptable maximum difference of 8° C, which is, considering the complexity of the system and its cooling, extremely valuable for proving thermal modeling methodology. Additionally, the designed enhanced gate-driver (eGD) successfully deals with electromagnetic interference (EMI) issues caused by having high slew rate voltage transients. The designed MV power cell (shown in Fig. 1) for utilization in modular multilevel (MMC) applications having the latest 10 kV SiC MOSFET half-bridge (HB) module achieved power density (PD) ≥ 10 kW/l, η ≥ 99% (shown in Fig. 2) and successfully operated at Vdc = 6 kV, I = 84 A, fsw ≥ 5 kHz, Tj ≤ 150° C in both both dc‐dc and dc‐ac mode, having high switching speeds up to dv/dt ≈ 100 V/ns.