LIBRARY

Analysis of Parasitic Capacitor's Impact on Voltage Sharing of Series-Connected SiC MOSFETs and Body-Diodes

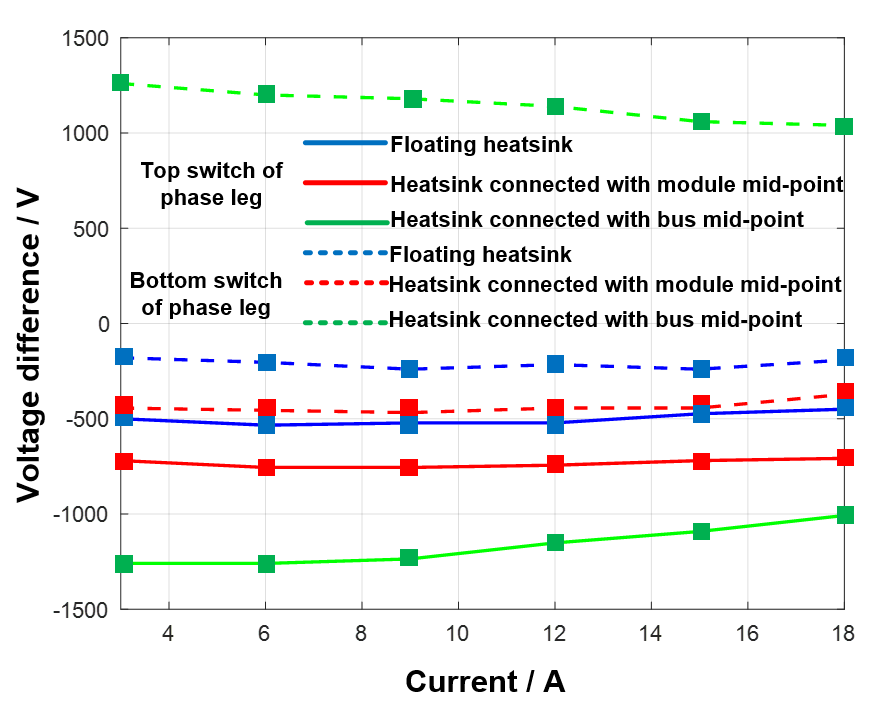

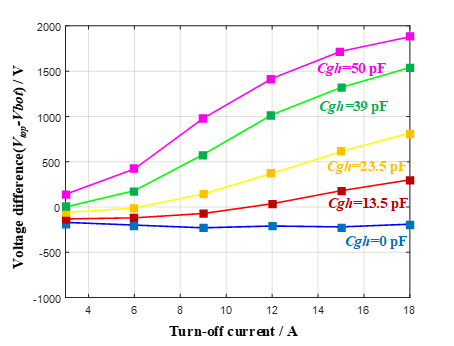

In this work, the impact of parasitic capacitor is analyzed. Drain/source to heatsink/baseplate parasitic capacitors and heatsink to dc-bus parasitic capacitors will introduce extra drain-source parasitic capacitors across devices, and the value of parasitic capacitor difference changes under different heatsink connection schemes and locations. The devices connected directly to the dc-bus terminals have the larger parasitic drain-source capacitor caused by the heatsink/baseplate. The gate parasitic capacitor will result in an extra gate current during the transient, and the current difference is not affected under different heatsink connections or locations. The top device (M1 and M3 in Fig. 1) in the series-connected devices always has an extra discharge current through the gate parasitic capacitor.

The voltage sharing of series-connected 10 kV SiC MOSFETs under different conditions is shown in Fig. 1 and Fig. 2. Under low load-current conditions, all load current charges the Coss of MOS- FETs. The voltage difference is affected mostly by drain-source parasitic capacitors. Gate parasitic capacitors have a limited impact under low load-current conditions. Under high load-current conditions, the parasitic capacitors affect the gate Miller plateau voltage level.

A larger drain-source capacitor results in a lower Miller plateau voltage, which helps equalize the dv/dt of the two devices. The gate parasitic capacitors always result in a lower Miller plateau voltage for the top device in series-connection and consequently results in a higher dv/dt for the top device.